信号发生器DAC芯片实现D/A转换方案加工

2020-10-13 17:49:16分类:技术专题2329

信号发生器在通信领域的应用,不仅要求信号发生器具有较高的稳定性和精度,还要能快速切换频点。本信号发生器PCBA方案采用可编程门阵列(FPGA)设备与高速D/A芯片相结合,采用直接数字合成技术(DDS法)产生连续波信号。DDS技术是从相位出发合成波形的技术,打破了传统频率合成技术的束缚,与传统频率合成方法相比具有频率分辨率高、输出相位噪音低、相位连续变化和转换速度快等多种优点,是全数字技术的关键随着微电子技术和数字集成电路的发展,近年来DDS技术发展迅速,广泛应用于数字通信系统。

原理

利用FPGA完成DDS核的功能,通过并串转换技术产生两路数字波形数据,并以低压差分模式(LVDS)输出,送入到DAC芯片。最终由DAC芯片经过数模转换后输出一定频率的模拟信号。

DDS信号产生单元

DDS的工作原理如图

主要包括相位累加器、波形存储器(ROM)、D/A转换器和低通滤波器四个部分。其中相位累加器与波形存储由FPGA完成。

在FPGA参考时钟的上升沿,相位累加器对频率控制字进行累加,得到相位对ROM寻址,完成相位一幅度转换,读取出相应的波形数据,经D/A转换输出阶梯波。

D/A转换

该方案D/A转换采样样率高达2.5GSPS,射频输出。

DAC芯片的采样频率设计为2GSPS,主机驱动解交错数据以偏移二进制的格式送到这两个接口,每路数据的频率均为芯片时钟频率的1/2,即为1GHz。嵌入式DDR数据时钟输入端口(DCI),主机在DCI时钟的上、下边沿均输出数据,DCI时钟频率为500MHz。DCI的时钟沿必须与数据位跃迁重合。输人数据的标称采样点是DCI时钟沿的中点,该点对应于数据眼的中心。同时为实现主机对DAC的同步操作,参考时钟4分频后经DCO接口送到主机,该频率与DCI时钟频率相同。

数据汇编器对接收来的两路1GHz的数据流进行重组,并在DAC核中进行数据重构,最终转换为模拟信号。

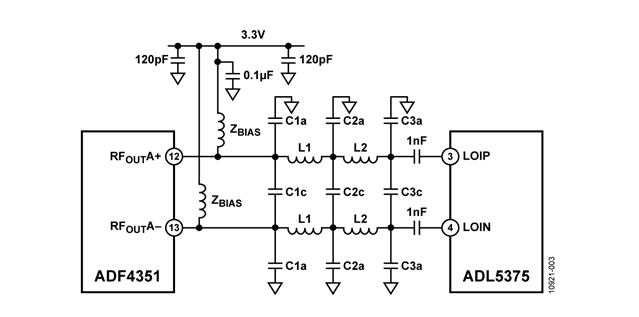

外围电路

REFIN输入一个参考频率,经过分频后作为鉴相频率与鉴相器N分频后的频率比较,鉴相器输出与相位误差成比例的电压,经过外部的环路滤波器控制带内外噪声与杂散,得到调谐电压,通过VCO使输出频率与设定值相同。输出同样是差分信号,经过三端滤波电容连接到时钟输入端口,为其提供稳定的工作频率。

奥芯科技是专业从事电子产品设计、电子方案开发、电子产品PCBA加工的深圳电子方案公司,主要设计电子产品包括工控、汽车、电源、通信、安防、医疗电子产品开发。

公司核心业务是提供以工控电子、汽车电子、医疗电子、安防电子、消费电子、通讯电子、电源电子等多领域的电子产品设计、方案开发及加工生产的一站式产品研发生产服务,为满足不同客户需求可提供批量产品加工。